Логическое проектирование и минимизация

| Категория реферата: Рефераты по информатике, программированию

| Теги реферата: стандарты реферата, реферат на тему право

| Добавил(а) на сайт: Антиох.

Предыдущая страница реферата | 8 9 10 11 12 13 14 15 16 17 18 | Следующая страница реферата

Представленные ниже электрические схемы являются примерами схем синтезируемых в ходе выполнения лабораторной работы.

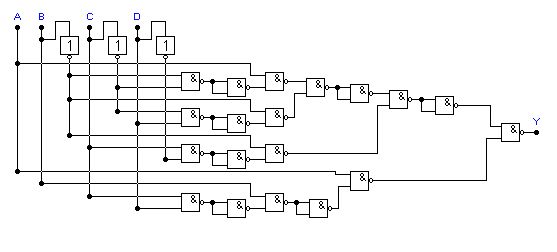

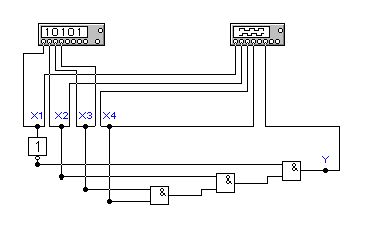

4.1 Схема цифрового автомата

Рис.4.1 Логическая схема к 1-му варианту

Схема изображённая на рис.4.1 представляет из себя цифровой автомат (с 4-мя входами A, B, C и D и выходом Y) реализующий логическое уравнение:

Y=ABC+BCD+BCD+ABCD

Настоящая схема реализована в базисе И-НЕ при помощи логического конвертора.

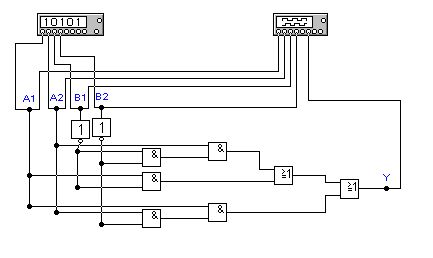

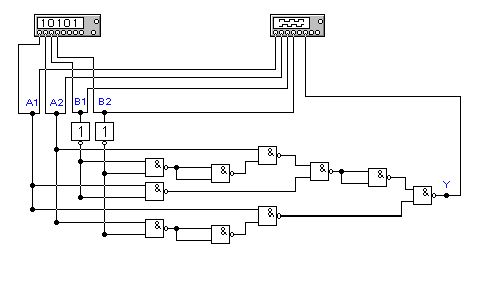

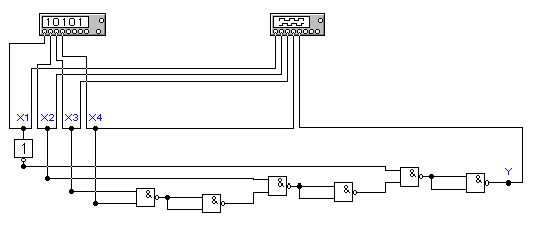

4.2 Цифровой компаратор 2-х разрядного кода

а)

б)

Рис.4.2 Схема цифрового компаратора ко 2-му варианту

На рис.4.2(а,б) изображена схема цифрового компаратора. Входными кодами являются 2-х разрядные коды А и В (А1,А2 и В1, В2 соответственно). Реализуемая им логическая функция имеет вид:

BСхема реализована в двух доступных в логическом конверторе базисах: рис.4.2(а) И, ИЛИ, НЕ и рис.4.2(б) И-НЕ. Для контроля правильности работы компаратора в обе схемы введены генератор слов и логический анализатор. Генератор слов подключен на входах схем и используется для генерации всех возможных комбинаций кодов А и В (2 разряда код А и 2 код В всего 4, следовательно 24=16 - генерируется 16 различных слов). На выходах схем подключен логический анализатор причём его первые 4 канала включены параллельно 4 используемым выходам генератора слов. Это сделано для получения более наглядной картинки на экране панели управления логического анализатора(см рис.4.3)

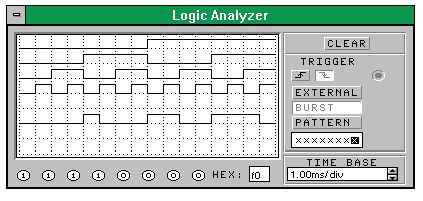

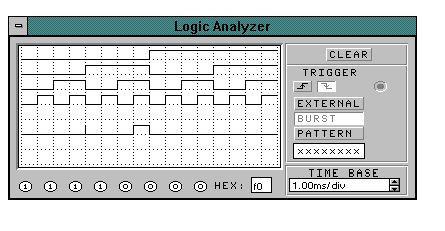

Рис.4.3 Временная диаграмма работы цифрового компаратора

Выход схемы подключен к 6-му каналу анализатора. Таким образом на экране одновременно отображаются входные и выходные сигналы, что позволяет получить полную временную диаграмму работы устройства(вход и выход на экране точно синхронизированы во времени).Наименование каналов сверху вниз: А1, А2, В1, В2 и Y.

4.3 Дешифратор 4-х разрядного адреса

а)

а)

б)

б)

Рис.4.4 Схема дешифратора адреса к 3-му варианту.

На рис.4.4(а,б) показана схема дешифратора адреса. Причём на рис.4.4(а) схема синтезирована в базисе И, ИЛИ, НЕ, а на рис.4.4(б) в базисе И-НЕ. Дешифрируемый адрес 01112 или 710. Подключив на вход схем генератор слов, а на выход логический анализатор(точно также как и в предыдущей схеме) легко получить временные диаграммы работы устройства см.рис.4.5

Рекомендуем скачать другие рефераты по теме: бесплатные рефераты на тему, курсовик.

Категории:

Предыдущая страница реферата | 8 9 10 11 12 13 14 15 16 17 18 | Следующая страница реферата

Главная

Главная